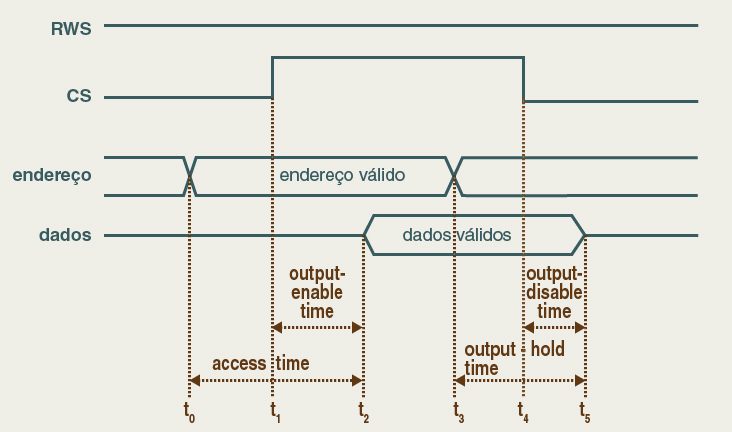

A maneira como é organizada a memória RAM impacta em restrições no tempo das operações de leitura e escrita. Por exemplo, como o caminho crítico da entrada a saída passa pelo decodificador, as entradas de endereço necessitam estar estáveis antes de qualquer outro sinal ou sinais. Isso quer dizer que, durante o ciclo de leitura mostrado na figura 13 abaixo, as entradas de endereço deverão ser fornecidas em t0, seguidas por CS em t1. Sendo assim, os dados da memória estarão disponíveis apenas em t2.

O atraso t2 – t0 é chamado memory-access time (tempo de acesso à memória), enquanto que o tempo t2-t1 é chamado output-enable time (tempo de habilitação da saída). Observe que depois de os valores das entradas de endereço terem sido alterados em t3, os dados continuam disponíveis até t5. O intervalo t5 – t3 é chamado output-hold time (tempo de manutenção da saída). O intervalo t5 – t4 é chamado de output-disable time (tempo de desabilitação da saída).

Em virtude de o caminho entre as entradas de endereço e as saídas ser maior do que o caminho entre CS até as saídas, o tempo de acesso aponta a validade dos dados sempre que o endereço e CS forem aplicados ao mesmo tempo. Em contrapartida, caso o endereço e CS não sejam mais válidos (CS igual a zero), o tempo de desabilitação especificará a validade dos dados.