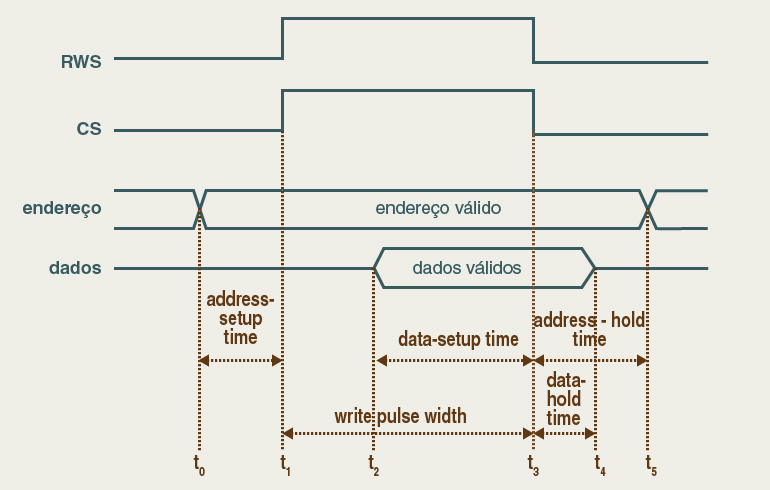

A Figura 14 é possível ver as restrições temporais para a situação de um ciclo de escrita em uma memória RAM. Nesta figura observa-se por premissa que CS e RWS foram aplicados, ao mesmo tempo, no instante t1. Em virtude de atraso entre o endereço e a saída ser maior do que o atraso entre CS ou RWS e a saída, o endereço deve ser aplicado um tempo antes, que neste caso, seria em t0.

O atraso t1–t0 é chamado de address setup time (tempo de preparação do endereço). Em virtude de cada CM ser feito a partir de um latch D controlado com CS exercendo a função de controle, cada bit do dado na borda de descida de CS (t3) será armazenado no correspondente latch. Contudo, é preciso que o dado já esteja estável um período antes e logo depois da borda de descida de CS para garantir a referida escrita. Observe a figura e veja que os tempos são descritos como data setup time (tempo de preparação do dado) e data hold time (tempo de manutenção do dado), sendo chamados respectivamente como: t3–t2 e t4–t3.

Cabe salientar que CS ou RWS devem ter duração igual ou superior ao intervalo de tempo t3–t1, que é chamado de write-pulse width (duração do pulso de escrita). Também é importante saber que o endereço deve estar válido durante um tempo após a borda de descida de RWS ou CS. Este intervalo de tempo é denominado address-hold time (tempo de manutenção do endereço), que pode ser demonstrado na imagem como t5–t3.