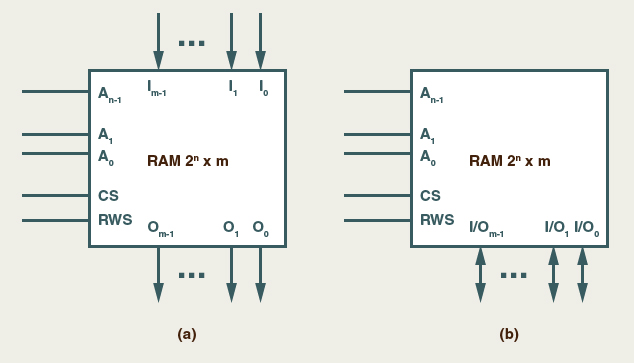

Vamos supor que uma empresa irá fabricar apenas um circuito integrado (CHIP) em uma memória RAM com capacidade de armazenamento 2n x m bits, conforme a organização que vimos anteriormente. A figura abaixo (Figura 10) é uma representação do chip que falamos agora. Este chip precisar ter “n” entradas de endereço (Na-1, ... , A1,A0), de tal maneira que seja possível selecionar uma e apenas uma dentre todas as 2n posições que há na matriz. Este chip poderá também conter “m” entradas (In-1 , ... , I1, I0), e “m” saídas (On-1 , ... , O1, O0 ), de tal maneira que seja possível a leitura/consulta do conteúdo de uma das 2n linhas ou a gravação/escrita de uma informação nova em uma das 2n linhas da matriz.

Em virtude de haver duas operações possíveis, leitura e escrita, sobre o conteúdo da matriz, é perfeitamente normal existir uma entrada de seleção da operação. Este tipo de entrada chamará RWS (Read/Write Select).

Figura 10

Em suma, há a necessidade de haver um sinal de habilitação do chip (CS-Chip Select). Para exemplificar, se o CS for igual a zero (CS=0) é porque o chip está desativado. O mesmo seria se o CS for igual a um (CS=1), é por que o chip está realizando uma operação determinada pelo valor da entrada RWS.